1 Introduction to computer architecture: (download)

- Computer Abstractions,

- Understanding Software and Hardware interface

2 Importance of Open Processor: (download)

- Basic Component of Processor Architectures

- ALU, Registers, Control, Data and Address Bus, ISA, Program and Data Memory

3 Processor Architectures: (download)

- Single Cycle

- Pipe-lined, Multi-Cycle

- Out-of-Order and Super-scalar

4 Data and Control Path of RISC-V ISA

- Pipeline Processor Architecture

- Data and Control Hazards

- Advanced and Complex Instructions Sets and Integration in Processor

5 Programming Processor using Assembly and C Language (download)

- Arithmetic, Logic,

- Read/Write and Branch Instructions

6 Memory Hierarchy Design, SRAM, DRAM, Cache Memories, Types of caches (download)

7 Cache Architecture and Memory Interfacing (download)

9 Memory Mapping and Input Output Addressing Scheme (download)

10 Memory Management Unit and Virtual Memory (download)

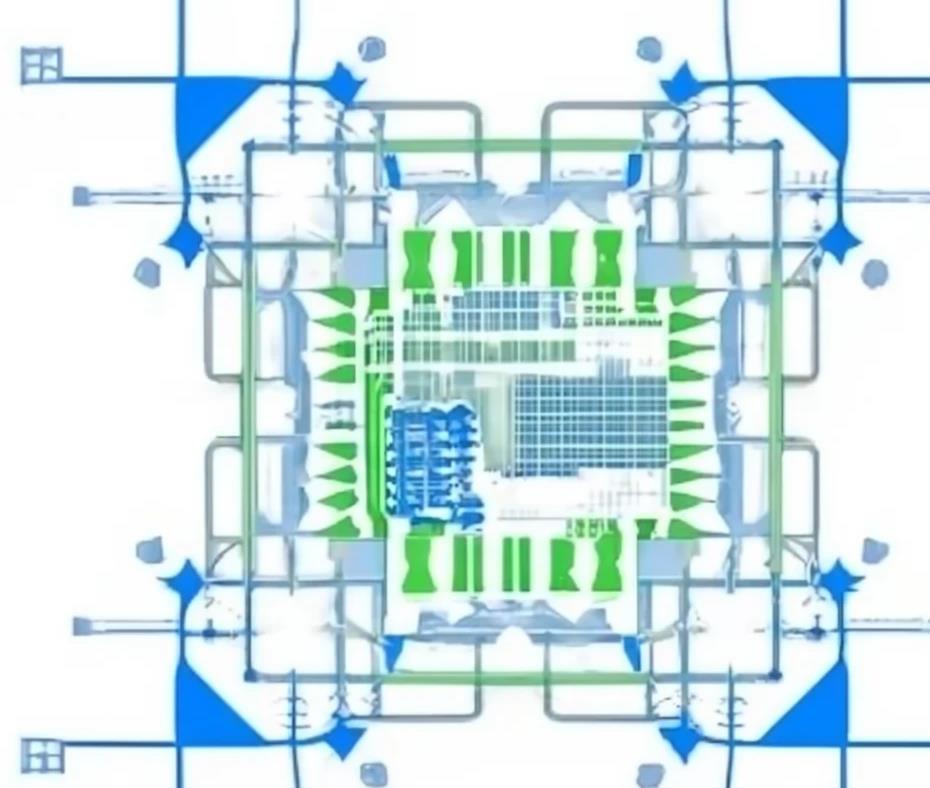

11 System on a Chip Architecture (download)

12 Different types of Computer Architectures (download)

13 Programming Computer Architectures (download)

- C/C++,

- Compilers

- Operating Systems

14 Single Core and Multi-core Programming (download)

15 Parallel Processing Multi-Tasking and Multi-Threading (download)

Commnads:

iverilog ./Processor_tb.v -o single_cycle.o

vvp ./single_cycle.o

gtkwave ./output_wave.vcd

Helping Material

RISCV Instruction Set

Introduction to STM32

Settingup Software (Kiel)

Programming GPIOs

1. Overview of ARM Cortex-M General Purpose InputOutput Module

2. Coding Developing GPIO Driver Using Information from the Datasheet

3. Coding Controlling GPIO using the BSRR Register

4. Coding Reading GPIO Inputs

Configuring UART (Serial Communication)

1. Overview of the UART Protocol

2. Coding Developing the UART Driver Using Information from the Datasheet

3. Coding Receiving Data with the UART

4. Coding Two-way UART Communication

Digital Design and Computer Architecture: RISC-V Edition (link)

The RISC-V Instruction Set Manual: Volume I: User-Level ISA (Download Link)

RISC-V Assembly Language Programming: Unlock the Power of the RISC-V Instruction Set (Download Link)

Understanding Computer Organization: A Guide to Principles Across RISC-V, ARM Cortex, and Intel Architectures (Download Link)

RISC-V Assembly Language Programming. Using ESP32-C3 and QEMU (Download Link)

Linux for Embedded and Real-time Applications, Fourth Edition (Download Link)

How to Develop Embedded Software Using The QEMU Machine Emulator (Download Link)

Embedded Linux Primer: A Practical Real-World Approach (Download Link)

Embedded Systems: Real-Time Interfacing to ARM Cortex-M Microcontrollers (Download Link)

Analog Interfacing to Embedded Microprocessors Real World Design (Download Link)

ARM microprocessor systems: Cortex-M architecture, programming, and interfacing (Download Link)

Raspberry Pi Retail Applications: Transform Your Business with a Low-Cost Single-Board Computer (Download Link)

[1]. Computer Organization and Design RISC-V Edition: The Hardware Software Interface 1st Edition by

David A. Patterson[1]. Computer Organization and Design RISC-V Edition: The Hardware Software Interface 1st Edition by

David A. Patterson

He is a permanent faculty member at, Riphah International University.

He did his Ph.D. from Barcelona-tech Spain, in collaboration with Barcelona Supercomputing Center and Microsoft Research Center.

He is a member of HiPEAC: European Network on High Performance and Embedded Architecture and Compilation, Barcelona Supercomputing Center and Microsoft ResearchCentre Spain.

Until January 2018, he had more than 14 years of industrial experience including, Barcelona Supercomputing Centre Spain, Infineon technology France, Microsoft Research Cambridge, PLDA Italia, IBM Zurich Switzerland, and REPSOL Spain. He has published more than 50 international publications and filed 5 patents.

Tassadaq's main research lines are Machine Learning, Parallel Programming, Heterogeneous Multi-core Architectures, Single board Computers, Embedded Computer Vision, Runtime Resource Aware Architectures, Software Defined Radio and Supercomputing for Artificial Intelligence and Scientific Computing.

www.tassadaq.ucerd.com

This course explores the principles of computer architecture through the RISC-V instruction set. Students will learn about instruction set design, performance optimizations, and modern multi-core and memory hierarchy techniques specific to RISC-V systems. The course equips students with the skills to understand and develop open hardware system on chip computer architecture, optimize applications and address computationally intensive problems using the RISC-V ISA.

Learning Outcomes:

1. Describe the performance of different Processor Architectures and how design trade-off improves performance.

2. Analyze the data-path and control of single-cycle and Multi-cycle architecture, and performance enhancement by pipelining using open-source compilers, simulators and emulators.

3. Design a Processor System on Chip architecture having cache and main memory unit.